Unidad aritmética de punto flotante: diseño e implementación con portabilidad

Floating point unit: design and implementation with portability

Barra lateral del artículo

Términos de la licencia (VER)

Esta obra está bajo una licencia internacional Creative Commons Atribución-NoComercial-SinDerivadas 4.0.

Declaración del copyright

Los autores ceden en exclusiva a la Universidad EIA, con facultad de cesión a terceros, todos los derechos de explotación que deriven de los trabajos que sean aceptados para su publicación en la Revista EIA, así como en cualquier producto derivados de la misma y, en particular, los de reproducción, distribución, comunicación pública (incluida la puesta a disposición interactiva) y transformación (incluidas la adaptación, la modificación y, en su caso, la traducción), para todas las modalidades de explotación (a título enunciativo y no limitativo: en formato papel, electrónico, on-line, soporte informático o audiovisual, así como en cualquier otro formato, incluso con finalidad promocional o publicitaria y/o para la realización de productos derivados), para un ámbito territorial mundial y para toda la duración legal de los derechos prevista en el vigente texto difundido de la Ley de Propiedad Intelectual. Esta cesión la realizarán los autores sin derecho a ningún tipo de remuneración o indemnización.

La autorización conferida a la Revista EIA estará vigente a partir de la fecha en que se incluye en el volumen y número respectivo en el Sistema Open Journal Systems de la Revista EIA, así como en las diferentes bases e índices de datos en que se encuentra indexada la publicación.

Todos los contenidos de la Revista EIA, están publicados bajo la Licencia Creative Commons Atribución-NoComercial-NoDerivativa 4.0 Internacional

Licencia

![]()

Esta obra está bajo una Licencia Creative Commons Atribución-NoComercial-NoDerivativa 4.0 Internacional

Contenido principal del artículo

Resumen

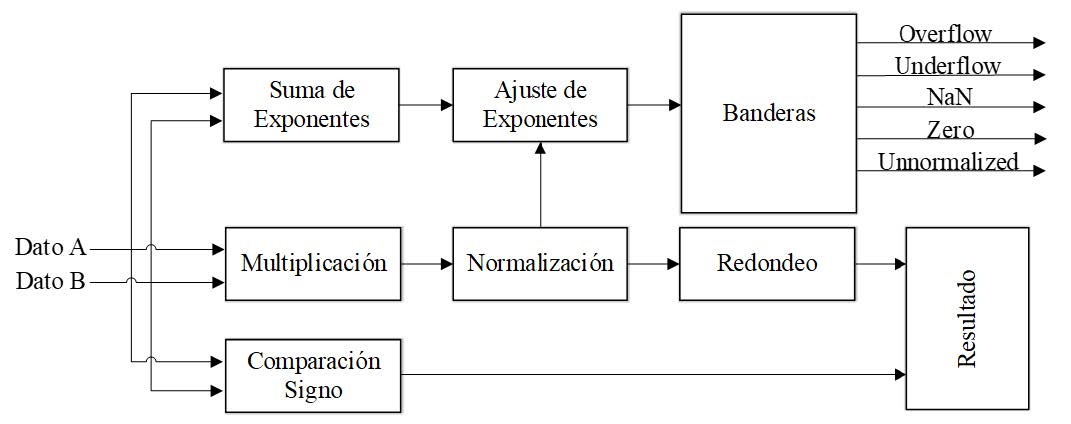

El uso de las unidades de punto flotante (FPU) en el procesamiento digital se ha incrementado dada la alta precisión y rango de números que se pueden representar. En el procesamiento de imágenes, filtros digitales con respuesta infinita al impulso (IIR), respuesta finita al impulso (FIR) y controladores digitales, se requieren este tipo de unidades para obtener resultados más precisos y evitar respuestas inestables, sin embargo, para implementar estas, algunos procesadores tienen unidades incorporadas lo que implica una dependencia tecnológica de los fabricantes para desarrollar prototipos. Para evitar dicha dependencia, en este artículo se presenta el diseño de los módulos para las operaciones más usadas en el procesamiento digital de señales: multiplicación y la suma/resta. Se presentan los pasos y consideraciones a tener en cuenta como las excepciones, redondeo y normalización de operandos, para lograr implementar estas operaciones en cualquier matriz de puertas lógicas programables en campo (FPGA). Se comprueban resultados utilizando el banco de pruebas MODELSIM® y se determinó la tasa de error, utilizando MATLAB®.

Descargas

Detalles del artículo

Referencias (VER)

Álvarez, J. A. y Lindig B., M. (2008) ‘Diseño de un Coprocesador Matemático de Precisión Simple usando el Spartan 3E’, Polibits, 38. Available at: https://www.redalyc.org/articulo.oa?id=402640451010.

Barry, P. y Crowley, P. (2012) ‘Chapter 5 - Embedded Processor Architecture’, in Barry, P. and Crowley, P. B. T.-M. E. C. (eds). Boston: Morgan Kaufmann, pp. 99–152. doi: https://doi.org/10.1016/B978-0-12-391490-3.00005-9.

BOLAÑOS, F. y BERNAL, Á. (2008) ‘Una implementación hardware optimizada para el operador exponenciación modular.’, Dyna, (156), pp. 55–63.

Cantoro, R. et al. (2016) ‘In-field functional test programs development flow for embedded FPUs’, 2016 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, DFT 2016, pp. 107–110. doi: 10.1109/DFT.2016.7684079.

Cervantes, A. et al. (2016) ‘Implementation of an open core IEEE 754-based FPU with non-linear arithmetic support’, in 2016 IEEE 36th Central American and Panama Convention (CONCAPAN XXXVI), pp. 1–6. doi: 10.1109/CONCAPAN.2016.7942354.

Chong, Y. J. y Parameswaran, S. (2011) ‘Configurable Multimode Embedded Floating-Point Units for FPGAs’, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 19(11), pp. 2033–2044. doi: 10.1109/TVLSI.2010.2072996.

Condia, J. E. R. et al. (2020) ‘Design and Verification of an open-source SFU model for GPGPUs’, in 2020 17th Biennial Baltic Electronics Conference (BEC), pp. 1–6. doi: 10.1109/BEC49624.2020.9276748.

Guerrero-Balaguera, J.-D., Condia, J. E. R. y Reorda, M. S. (2021) ‘On the Functional Test of Special Function Units in GPUs’, in 2021 24th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), pp. 81–86. doi: 10.1109/DDECS52668.2021.9417025.

Hamid, L. S. A. et al. (2010) ‘Design of Generic Floating Point Multiplier and Adder/Subtractor Units’, in 2010 12th International Conference on Computer Modelling and Simulation, pp. 615–618. doi: 10.1109/UKSIM.2010.117.

José, W. et al. (2014) ‘Efficient implementation of a single-precision floating-point arithmetic unit on FPGA’, in 2014 24th International Conference on Field Programmable Logic and Applications (FPL), pp. 1–4. doi: 10.1109/FPL.2014.6927391.

Joshi, M. N. y Gawali, D. H. (2016) ‘Floating point unit core for Signal Processing applications’, in 2016 Online International Conference on Green Engineering and Technologies (IC-GET), pp. 1–6. doi: 10.1109/GET.2016.7916650.

Karlstrom, P., Ehliar, A. y Liu, D. (2008) ‘High-performance, low-latency field-programmable gate array-based floating-point adder and multiplier units in a Virtex 4’, IET Computers & Digital Techniques, 2(4), pp. 305–313. doi: 10.1049/iet-cdt:20070075.

Kaur, P. et al. (2015) ‘Double Precision Floating Point Arithmetic Unit Implementation- A Review’, International Journal of Engineering Research & Technology (IJERT), 4(7), pp. 992–994. Available at: http: / /dx.doi.org/10.17577/IJERTV4IS070766.

Lasith, K. K. y Thomas, A. (2014) ‘Efficient implementation of single precision floating point processor in FPGA’, in 2014 Annual International Conference on Emerging Research Areas: Magnetics, Machines and Drives (AICERA/iCMMD), pp. 1–5. doi: 10.1109/AICERA.2014.6908269.

López, J., Restrepo, J. y Tobón, J. (2020) ‘Parametric Decimal Division using Hardware Description Language’, Revista EIA, 17, pp. 1–6. doi: https://doi.org/10.24050/reia.v17i33.1318.

Malkapur, S. B. y Rajput, R. P. (2020) ‘Design of Generic Floating Point Pipeline Based Arithmetic Operation for DSP Processor’, in 2020 Second International Conference on Inventive Research in Computing Applications (ICIRCA), pp. 1059–1064. doi: 10.1109/ICIRCA48905.2020.9182948.

Ramyarani, N. Subbiah, V. Deepa, P. (2019) ‘Design of area-efficient IIR filter using FPPE’, Turkish Journal of Electrical Engineering & Computer Sciences, 27(3), pp. 2321–2330. doi: :10.390.

Russinoff, D. M. (2019) Formal Verification of Floating-Point Hardware Design. first edit. Austin, TX, USA: Springer. doi: 10.1007/978-3-319-95513-1.

Sandoval-Ruiz, C. (2019) ‘Modelo VHDL de Control Neuronal sobre tecnología FPGA orientado a Aplicaciones Sostenibles ’, Ingeniare. Revista chilena de ingeniería . scielocl , pp. 383–395.

STALLINGS, W. (2005) Organización y arquitectura de computadores. Séptima Ed. Madrid: PEARSON EDUCACIÓN.

Veeranki, Y. R. and Nakkeeran, R. (2013) ‘Spartan 3E Synthesizable FPGA Based Floating-Point Arithmetic Unit’, International Journal of Computer Trends and Technology (IJCTT), 4, pp. 751–755. Available at: www.ijcttjournal.org.

Wilton, C. Y. A. M. S. W. L. P. H. W. L. S. J. E. (2012) ‘Optimizing Floating Point Units in Hybrid FPGAs’, IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, 20(7), pp. 1295–1303. doi: 10.1109/TVLSI.2011.2153883.

Zhang, B. y Zhao, J. (2017) ‘Elementary Function Computing Method for Floating-Point Unit’, Journal of Signal Processing Systems, 88(3), pp. 311–321. doi: 10.1007/s11265-016-1166-x.

Zoni, D., Galimberti, A. y Fornaciari, W. (2021) ‘An FPU design template to optimize the accuracy-efficiency-area trade-off’, Sustainable Computing: Informatics and Systems, 29, p. 100450. doi: https://doi.org/10.1016/j.suscom.2020.100450.

Artículos similares

- Julieth Katherin Acosta Medina, Maira Camila Paba Medina, Aura Cecilia Pedraza Avella, Modelo de negocios a partir de la cadena de valor industrial: Caso bioempaques de biomasa residual de cacao , Revista EIA: Vol. 21 Núm. 42 (2024): Tabla de contenido Revista EIA No. 42

También puede {advancedSearchLink} para este artículo.

PDF

PDF

FLIP

FLIP